베릴로그 A to Z (1) - EDA Playground 소개

안녕하세요,

이번 포스팅을 시작으로 Verilog HDL를 이용한 프로젝트를 연재해보려고 합니다.

Verilog는 전자 공학 또는 컴퓨터 공학을 전공한다면 배우게 되는 언어입니다. 이를 활용하여 Behavioral Model부터 Transistor Level에 이르기까지 실제 하드웨어 동작을 모델링할 수 있습니다.

실제로 대부분의 반도체 RTL 설계 및 검증 과정에서 Verilog가 사용되는데요, VHDL과 Verilog 둘 중 하나만 배운다면 Verilog를 배워두는게 좋다고 생각합니다.

프로젝트 진행을 하기 위해서는 다른 프로그래밍 언어와 마찬가지로 Verilog를 간편하게 Compile 하고 실행할 수 있는 환경이 필요한데요,

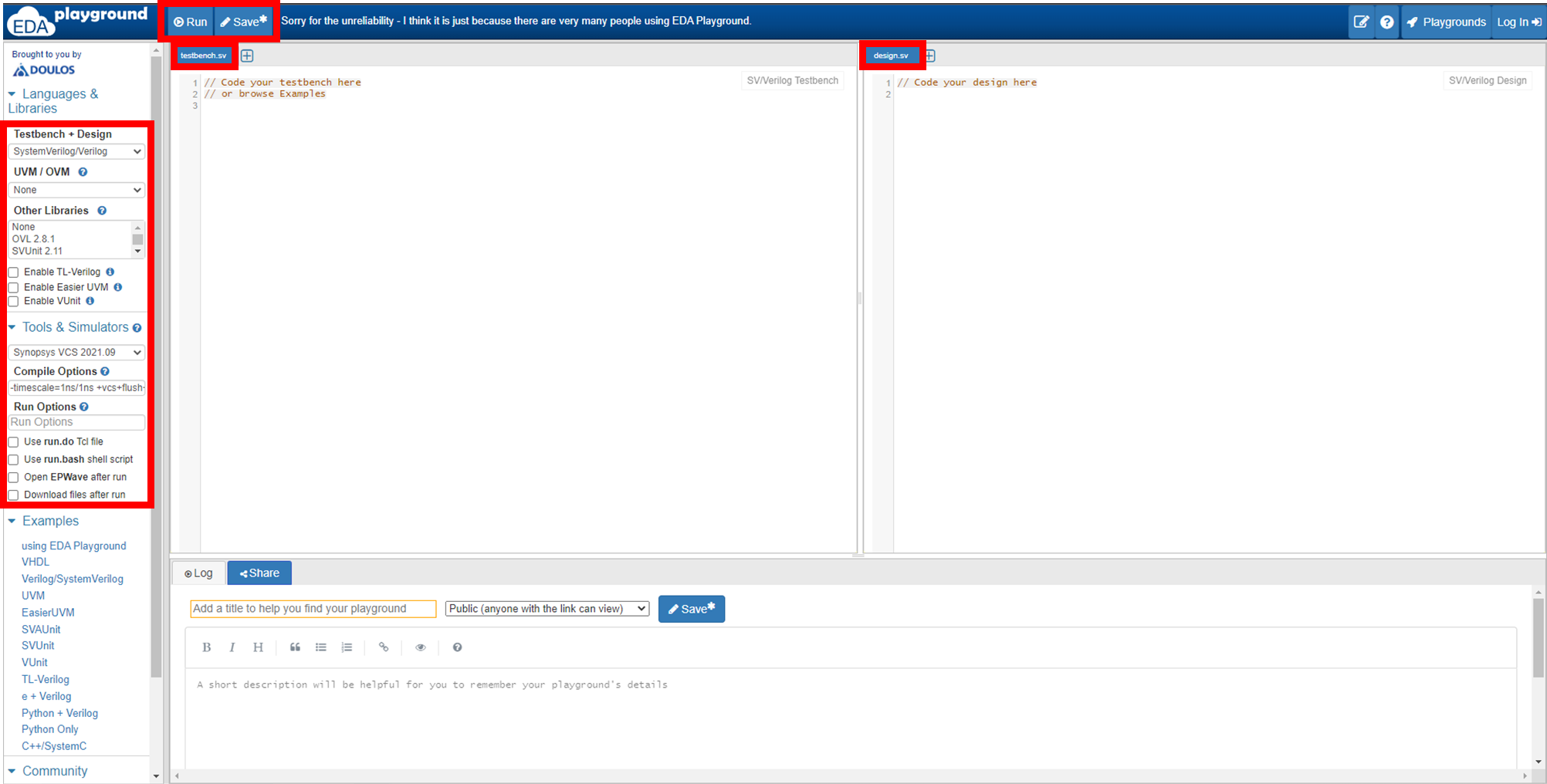

Synopsys, Cadence, Simens와 같은 EDA 회사의 Tool 설치 없이도 간편하게 Verilog를 실행할 수 있는 Editor 환경인 "EDA Playground"를 소개시켜드리겠습니다.

EDA Playground 소개

EDA Playground는 Doulos가 운영하는 Verilog를 위한 무료 Editor 환경입니다.

회원 가입을 하면 Synopsys, Cadence 그리고 Mentor의 Verilog 시뮬레이터를 사용할 수 있습니다.

특히, 현업에서 가장 많이 사용하는 Synonpsys VCS 21.09와 Cadence Xcelium 20.09를 무료로 이용할 수 있네요!

이외에도 최신버전의 UVM 라이브러리도 사용가능하며, Verilog 합성을 위한 툴도 제공하고 있습니다.

Verilog 외에도 Python, Perl, C/C++과 같은 프로그래밍 언어의 컴파일과 실행을 지원하지만, 해당 기능을 사용할 것 같진 않습니다.

화면 구성은 상당히 심플한데요,

왼쪽에는 Testbench, 오른쪽에는 DUT 코드를 작성하고 가장 좌측의 탭에서 사용할 Simulator를 선택한 후, 가장 상단의 Run을 클릭하면 시뮬레이션이 동작합니다.

마지막으로 결과는 가장 하단의 Log 창을 통해 확인이 가능하네요.

다만, 로그인을 한 후 계정인증을 받아야 Run이 가능해서 회사 이메일로 인증이 완료된 후에 프로젝트를 진행하도록 하겠습니다.

정리

사실, Verilog가 반도체 및 하드웨어 분야에 주로 사용되기 때문에

일반적으로 사용하는 프로그래밍 언어(C, JAVA, PYTHON 등)에 비해 양질의 자료를 찾기 힘든 편입니다.

따라서 "프로젝트로 배우는 베릴로그" 시리즈를 통해 실무에 바로 적용할 수 있는 Verilog 코딩 노하우를 공유할 계획입니다.

특히, 저는 Verilog의 가장 기본적인 문법만 숙지한 뒤 어떤 주제를 잡고 프로젝트를 하면서 다양한 문법을 익혀나가는 게 효과적이라고 생각합니다.

따라서 Verilog로 하나의 IP를 구현한 뒤, Testbench를 이용한 검증부터 SystemVerilog 및 UVM을 활용한 검증에 이르기까지 RTL(Register Transfer Level, 보통 베릴로그 코딩과 동일한 의미로 사용됩니다) 설계 및 검증 전체 Flow를 보여드리고자 합니다.

다음 포스팅도 많은 기대 부탁드립니다.

'지식 공유 > Verilog' 카테고리의 다른 글

| [Verilog] 베릴로그 A to Z (2) - Verilog/SystemVerilog/UVM LRM (3) | 2023.02.28 |

|---|

댓글