반응형

하드웨어 설계 검증에서 코너 케이스를 놓치지 않고 커버리지를 극대화하기 위한 가장 강력한 도구 중 하나는 바로 랜덤 테스트입니다. 이 글에서는 SystemVerilog에서 제공하는 Randomization 기능과 Constraints 사용법을 소개하고, 실무에서 어떻게 활용할 수 있는지 살펴봅니다.

랜덤 테스트가 필요한 이유

- Directed test는 기능 위주의 검증에는 효율적이지만 corner case 탐지에 한계가 있습니다.

- 반면 Constraint 기반 랜덤 테스트는 미처 생각하지 못한 상황까지도 포괄할 수 있는 가능성을 제공합니다.

Regression Test와 Random Test

- Regression Test: 동일한 시나리오를 다양한 입력 및 조건에서 반복 수행해 기능 이상 유무를 검증합니다.

- Random Test: 제약 조건을 부여해 랜덤하게 시나리오를 생성합니다. svseed를 고정하거나 랜덤하게 하여 동일 조건 반복 또는 다양한 상황 생성이 가능합니다.

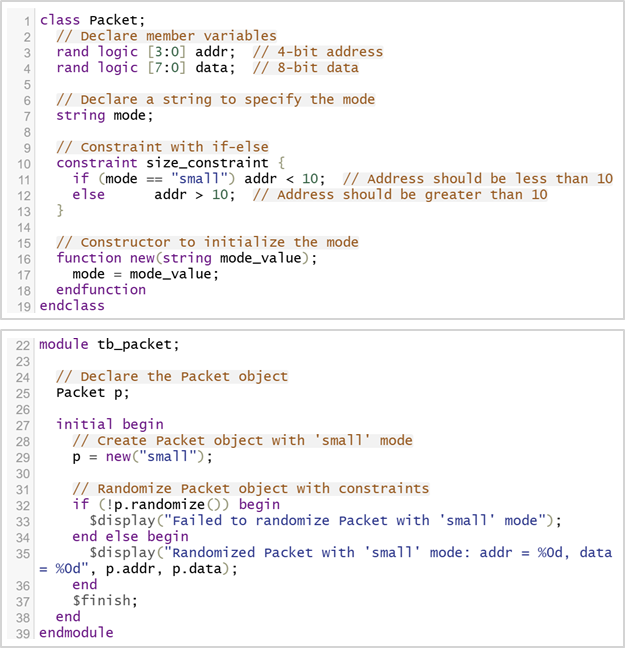

Constraint Blocks의 구성

SystemVerilog에서는 rand, randc 변수와 constraint 블록을 통해 유연한 제약 기반 랜덤화를 구현할 수 있습니다.

랜덤 변수의 종류

- rand: randomize() 호출 시마다 새로운 값 생성 (중복 가능)

- randc: 가능한 값이 모두 사용되기 전까진 중복 없음 (순환 랜덤화)

제약 표현 기법

- 기본 제약

constraint word_align { addr[1:0] == 2'b0; }

- 조건 제약 (If-Else)

constraint size_c { if (mode == "small") len < 10; else len > 100; }

- 암시적 제약 (Implication)

constraint imp_c { mode == "high" -> speed > 100; }

- 반복 제약 (foreach)

constraint iter_c { foreach (A[i]) A[i] inside {2, 4, 8, 16}; }

- 집합 포함 제약

constraint set_c { x inside {3, 5, [9:15]}; }

- 분포 제약

constraint dist_c { y dist {100 := 1, 200 := 2, 300 := 5}; }

- 소프트 제약 (soft)

- 소프트 제약은 다른 하드 제약에 의해 무시될 수 있는 우선순위 낮은 제약입니다.

constraint soft_c { soft priority == 1; }

Randomization Method

| 특징 | $random | $urandom | $urandom_range | std::randomize() |

| 타입 | 32-bit 정수 (signed) | 32-bit 정수 (unsigned) | 지정된 범위의 unsigned 정수 | 객체의 멤버 변수 값 |

| 범위 | -2^31 ~ 2^31-1 | 0 ~ 2^32-1 | 지정된 범위로 정수 생성 | 정의된 범위 내에서 임의 값 생성 |

| 사용 방식 | $random | $urandom | $urandom_range(min, max) | std::randomize() |

| 선언조건 | - | - | 최소값, 최대값 필요 | 객체에 대해 randomize 호출 |

In-line Constraints

- randomize() with 문법을 통해 테스트마다 제약 조건을 유연하게 추가할 수 있습니다.

- obj.randomize() with { len inside {[5:10]}; }

rand_mode()

- 특정 랜덤 변수의 랜덤화를 제어할 수 있습니다.

obj.rand_mode(0); // 전체 랜덤 비활성화

obj.var.rand_mode(1); // 개별 변수 활성화

constraint_mode()

- 제약 조건의 활성/비활성을 동적으로 제어합니다.

obj.constraint_mode(1); // 제약 활성화

obj.constraint_mode(0); // 제약 비활성화

Deep Talk: force-release 문법

- 시뮬레이션 중 특정 신호를 강제로 설정할 수 있습니다.

force signal = 1'b1;

release signal;- 활용 예시:

- 특정 조건에 강제 설정하여 코너 케이스 테스트

- DUT 출력 강제 고정 후 반응 확인

반응형

'지식 공유 > SystemVerilog' 카테고리의 다른 글

| [SystemVerilog 실무] 10. Assertion 이해 및 활용 (0) | 2025.05.10 |

|---|---|

| [SystemVerilog 실무] 9. Functional Coverage의 이해 (0) | 2025.05.10 |

| [SystemVerilog 실무] 8. Package와 Interface (0) | 2025.05.10 |

| [SystemVerilog 실무] 6. SystemVerilog OOP: 캡슐화, 상속, 다형성 (0) | 2025.05.10 |

| [SystemVerilog 실무] 5. SystemVerilog 클래스 기초 완전정복 (0) | 2025.05.10 |

| [SystemVerilog 실무] 4. 절차적 블록과 제어 구조 이해하기 (0) | 2025.05.10 |

댓글