반응형

SystemVerilog 설계 및 검증 흐름에서 가장 기본이자 중요한 개념 중 하나는 **절차적 블록(Procedural Blocks)**과 **제어 구조(Control Structures)**입니다. 본 포스트에서는 이를 중심으로 실무에 바로 활용 가능한 문법과 구조를 정리합니다.

절차적 블록 (Procedural Blocks)

SystemVerilog의 절차적 블록은 하드웨어의 **동작(behavioral)**을 기술하는 핵심 구조입니다.

- initial

- 시뮬레이션 시작 시 단 한 번만 실행

- testbench setup 등 초기화 용도에 자주 사용

- final

- 시뮬레이션 종료 직전에 한 번 실행

- 로그 출력이나 리소스 정리에 사용

- always

- 조건 없이 무한히 반복 실행

- 순차 논리 설계의 기본 구조

SystemVerilog는 다음과 같이 설계 목적에 맞게 세분화된 always 블록을 제공합니다:

- always_comb: 조합 논리 (combinational logic) 전용

- always_latch: 래치 생성을 위한 블록

- always_ff: 동기식 플립플롭(FF) 생성용

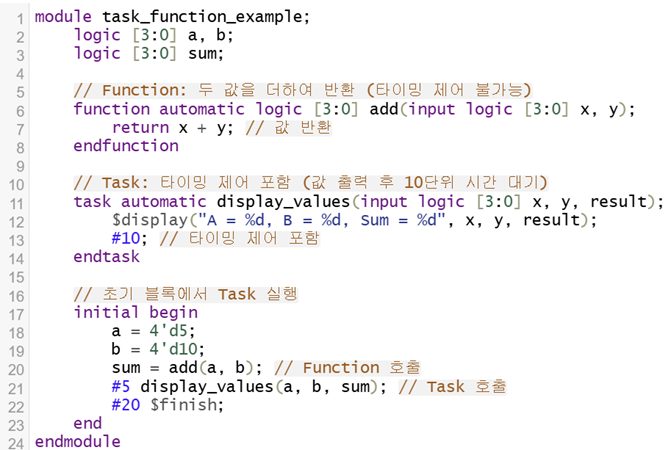

태스크(Task)와 함수(Function)

코드의 재사용성과 모듈화를 위한 구조입니다.

- task

- 타이밍 제어(예: @posedge clk, #5) 가능

- 여러 개의 출력 인자 지원

- 반환값 없음 → 프로시저 용도에 적합

- function

- 반드시 하나의 값을 반환해야 함

- 타이밍 제어 불가

- 빠른 연산이나 조합 논리 표현에 적합

✔︎ 인자 전달 방식

- Call by Value: 인자의 복사본을 전달 (원본 불변)

- Call by Reference: 참조(주소)를 전달하여 원본 변경 가능

const 키워드로 원본 보호 가능

function int add(int a, int b);

return a + b;

endfunction

task modify(ref int a);

a = a + 10;

endtask

선택 제어문 (Selection Statements)

- if-else

- 단일/복합 조건 분기 처리에 유용

- case

- 다중 조건 분기 시 가독성 좋음

if (a > b)

do_something();

else

do_something_else();

case (sel)

2'b00: out = x;

2'b01: out = y;

default: out = z;

endcase

| 구문 | 비트 값 처리 | x와 ? 처리 | 주요 특징 |

| case | 정확한 일치만 허용 | x와 ?는 일치하지 않는 값으로 취급 | 모든 값이 정확히 일치해야 함. |

| casex | x와 ?는 모든 값과 일치 (와일드카드) | x와 ?는 어떤 값에도 일치 (와일드카드) | x와 ?를 와일드카드로 처리하여 유연한 매칭 |

| casez | z는 0 또는 1로 취급, x와 ?는 와일드카드 | z는 0 또는 1로 취급, ?는 모든 값과 일치 | z는 0과 1로 처리되고, ?는 모든 값에 일치 |

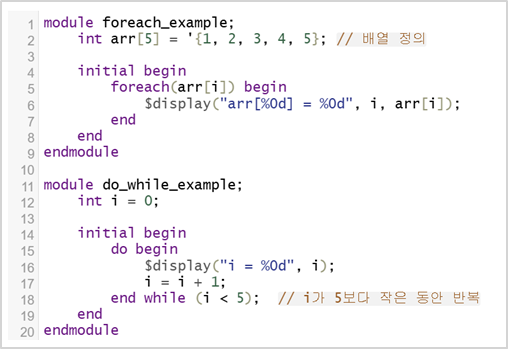

반복 제어문 (Loop Statements)

SystemVerilog는 다양한 반복 구조를 지원합니다.

- for / while / do...while : 일반적인 루프 제어

- repeat(n) : 명확한 반복 횟수 지정

- foreach : 배열, 구조체 등 컬렉션에 대해 순회

foreach (array[i])

$display("array[%0d] = %0d", i, array[i]);

블로킹 vs 넌블로킹 할당

- = (Blocking)

- 실행 순서를 보장

- <= (Non-blocking)

- 병렬적인 시뮬레이션 동작 반영

조합 논리에서는 블로킹을, 순차 논리(FF 기반 설계)에서는 넌블로킹 할당을 사용하는 것이 일반적인 베스트 프랙티스입니다.

타이밍 제어

- 지연 제어 (#): 고정 시간 지연

#5 a = b; - 이벤트 제어 (@): 특정 조건에서 대기

@(posedge clk) - wait: 조건 만족 시까지 대기

wait (ready == 1);

Named Block과 disable

begin : my_block

// 내용

end

disable my_block;

- 블록에 이름을 부여하고, 특정 블록을 비동기적으로 종료 가능

Event & Sequence

- event 변수

- ->ev;로 트리거, @ev로 대기

- sequence

- 여러 이벤트를 시퀀스화 하여 Assertion 등에 활용

sequence my_seq;

@(posedge clk) a ##1 b ##1 c;

endsequence

FSM (Finite State Machine) 코딩 스타일

- FSM (Finite State Machine, 유한 상태 기계)란?

- FSM(유한 상태 기계)은 정해진 유한한 개수의 상태를 가지며, 입력에 따라 상태가 변하고 특정 동작을 수행하는 디지털 논리 설계 개념

- FSM의 주요 구성 요소

- 상태(State): 시스템이 특정 시점에서 가지고 있는 상태

- 입력(Input): 외부에서 주어지는 신호 또는 이벤트

- 전이(Transition): 입력에 따라 상태가 변하는 과정

유형 출력 결정 방식 장점 단점

| Moore | 현재 상태만 | 안정성, 단순 | 반응 속도 느림 |

| Mealy | 상태 + 입력 | 빠른 반응 | 글리치 발생 가능성 |

SystemVerilog는 enum을 활용한 상태 표현으로 FSM 설계를 간결하게 할 수 있습니다.

반응형

'지식 공유 > SystemVerilog' 카테고리의 다른 글

| [SystemVerilog 실무] 7. 랜덤 테스트와 Constraints 기초 (0) | 2025.05.10 |

|---|---|

| [SystemVerilog 실무] 6. SystemVerilog OOP: 캡슐화, 상속, 다형성 (0) | 2025.05.10 |

| [SystemVerilog 실무] 5. SystemVerilog 클래스 기초 완전정복 (0) | 2025.05.10 |

| [SystemVerilog 실무] 4. 절차적 블록과 제어 구조 이해하기 (0) | 2025.05.10 |

| [SystemVerilog 실무] 2. 자료구조와 활용 (0) | 2025.05.10 |

| [SystemVerilog 실무] 1. 데이터 타입과 연산자 완전 정복 (0) | 2025.05.05 |

댓글